Source control is critical to reuse and scaleability of modular IP. Utilize libraries as much as possible to share common scripts and HDL modules between IP. parameter files, vendor IP) instead of storing the generated products. Temporary or generated files should not be stored, and make an effort to script the generation of files (i.e. Only keep the bare minimum files needed to reproduce the firmware IP in your source control managment system. The next section walks you through my approach to applying these best practices to my own design pattern using open source tools with Xilinx Vivado. Implement each concept from the beginning of the design cycle for maximum effectiveness. In order to mitigate the challenges I mentioned above, apply the following best practices to your firmware IP design flow in order to have a design pattern for modular firmware IP generation. Large organizations can support the staffing required for a solution with this sophistication, but the rest of us just don’t want to spend the time and money! Best Practices However, the complexity of this solution makes it prohibitive for tight schedules and budgets due to the large learning curves and infrastructure overhead.

Vivado hls gnu octave software#

OpenCPI is a great example of an open-source modular firmware design pattern, and it implements a common structure for embedded software designs as well. Too often reuse of a firmware module or IP involves a literal copy of the files! The final challenge I will mention here is that no unified standard exists for cataloguing and source control of IP and HDL libraries.

Vivado hls gnu octave manual#

The result is often a manual flow for regenerating IP – the Achilles heel of reuse. The heterogeneous toolset of firmware design can also make automation of IP building, simulation, and packaging a challenge. (Keep reading if you are feeling this pain!) These types of small updates are very common and result in multiple inefficient design iterations.

Vivado hls gnu octave update#

Now let’s say that you want to change the bit widths of your input! Using a manual design flow to update the bit widths, you will need to modify your HDL, regenerate the Xilinx Complex Multiplier IP core, update the Octave model, and update the QuestaSim simulation inputs.

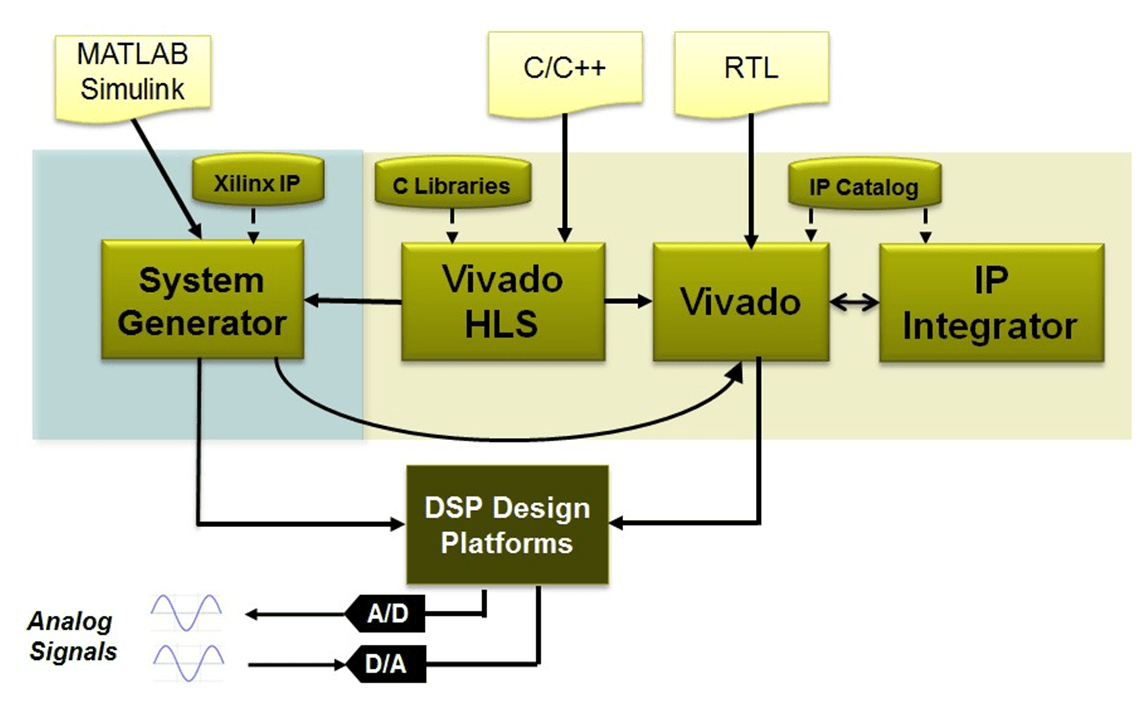

You are building/packaging your FIR filter with Xilinx Vivado, modeling the mathematical behavior with Octave, and simulating with Mentor Graphics QuestaSim. The modification of these parameters must be synchronized when reusing IP.įor example: Let’s say that you have developed a FIR filter firmware IP that uses a Xilinx Complex Multiplier IP core. Instead of a single IDE with an integrated compiler, parameters are scattered across HDL design files, modeling tools (MATLAB/Octave/Python), vendor tools (Vivado/Quartus/Libero), and simulation tools (QuestaSim/Cadence). Modularity relies heavily upon parameterization which can be a difficult challenge in firmware design. Due to long development cycles (and short schedules!), firmware designers often struggle to generate modular intellecutal property (IP) that is reusable between applications.

0 kommentar(er)

0 kommentar(er)